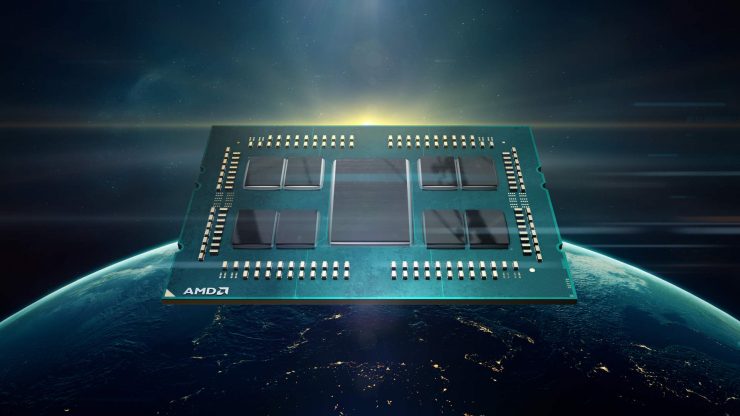

Sau khi ra mắt bộ xử lý thế hệ thứ tư.2 AMD EPYC 'ROMA', nơi có tổng số 9 mô hình, bây giờ chúng tôi biết rằng công ty đã không tạo ra ít hơn 15 CPU là khác nhau cho Gen-3 rửa tội như AMD EPYC Milan.

Nếu dữ liệu là chính xác, đỉnh của phạm vi mô hình sẽ nhập không ít hơn 10 người chết để thêm tối đa 80 lõi được cài đặt trong bộ điều khiển bộ nhớ Octa(8)– kênh, có nhiều biến thể với ít hạt nhân hơn, nhưng ở đâu Không gian trống này có thể được sử dụng bằng cách thêm bộ nhớ HBM để tăng đáng kể tốc độ với khuôn I / O đã biết. Bằng cách này, công ty có thể nhập có tới 10 người chết (80 lõi) với không gian cho 4 Chip nhớ HBM; và I / O DIe hoặc ví dụ chọn 8 chết đi (64 lõi) + 6 chết vì trí nhớ HBM + I / O Die, vì vậy công ty sẽ có nhiều quyền kiểm soát hơn đối với việc tùy chỉnh silicon.

Một thiết kế dựa trên interleaver (nhà môi giới) với bộ nhớ HBM tích hợp có thể cung cấp thời gian truy cập và chuyển tiền nhanh hơn nhiều thay vì bộ nhớ dựa trên DDR truyền thống, nơi các kênh DDR có thể hoạt động như một nút cổ chai. Với các kết nối, I / O và các bộ chuyển đổi, việc loại bỏ các cạm bẫy của việc liên kết CPU với bộ nhớ HBM sẽ dẫn đến khả năng tăng tốc đáng kể cho các ứng dụng phụ thuộc nhiều vào bộ nhớ, lưu ý rằng cấu hình này sẽ tạo ra tốc độ nhanh hơn nhiều so với bộ nhớ tiêu chuẩn chúng ta có. có ngay bây giờ, tức là RAM DDR4.

Điều đáng nói là những rò rỉ trước đây đã chỉ ra rằng AMD Milan có thiết kế 8 + 1es: 64 lõi + 1 Chip nhớ HBM, một bước khá hợp lý cho AMD do giới hạn bộ nhớ DDR4, điều mà DDR5 có thể giải quyết trong tương lai, vì vậy với bộ nhớ DDR5, chúng ta thậm chí có thể thấy CPU với 14 điểm chết (112 lõi) + Chết I / O.

thông qua: Wccftech