Hot Chips 31 Keynote Hari 2: Dr. Phillip Wong, Wakil Presiden Riset di TSMC (13:45 PT)

04:41 EDT – Keynote untuk hari kedua adalah dari TSMC, dengan Dr. Phillip Wong mengambil panggung untuk berbicara tentang perkembangan terbaru dalam penelitian dan portofolio TSMC. Pembicaraan dimulai pada 1:45 PT / 4:45 ET.

04:42 EDT – Semua orang kembali dari makan siang dan kami akan mulai dalam beberapa menit

04:43 EDT – Sesi terakhir ini akan membahas tentang TSMC, Gen-Z, TeraPHY, istirahat, kemudian Intel Lakefield, Xeon Jintide, dan Hololens 2.0 Silicon

04.47 EDT – Dr. Philip Wong, Wakil Presiden Riset Perusahaan, yang bertanggung jawab atas teknologi proses baru

16:48 EDT – Menghabiskan 16 tahun di IBM, lebih dari 600 makalah

16:48 EDT – Pembicaraan tentang teknologi, bukan tentang produk

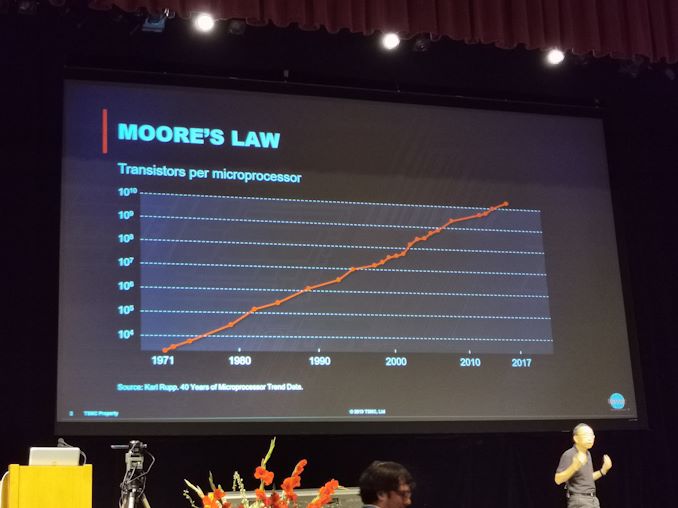

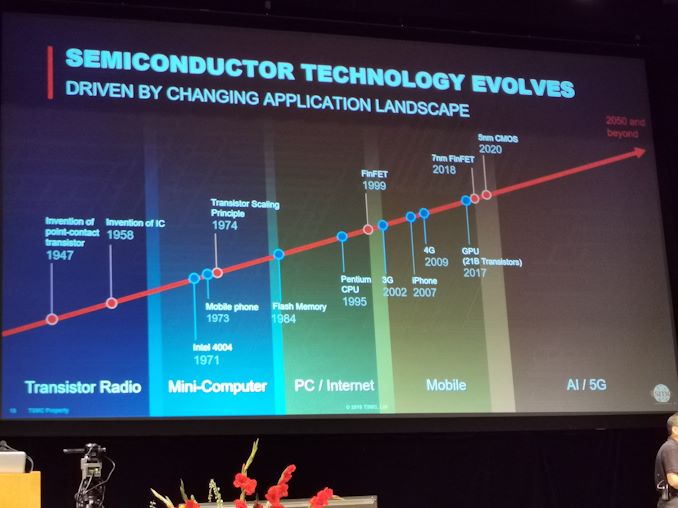

04.49 EDT – Hukum Moore, dari tahun 1971 hingga 2017

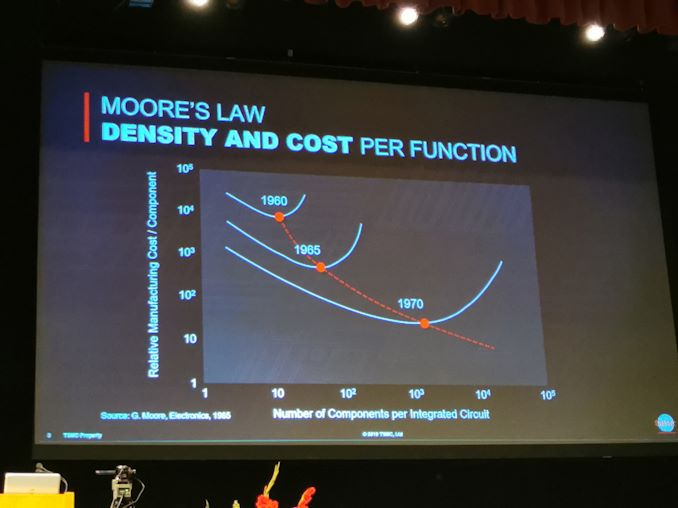

04.49 EDT – Hukum Moore adalah tentang kepadatan

04.49 EDT – Kertas asli Moore

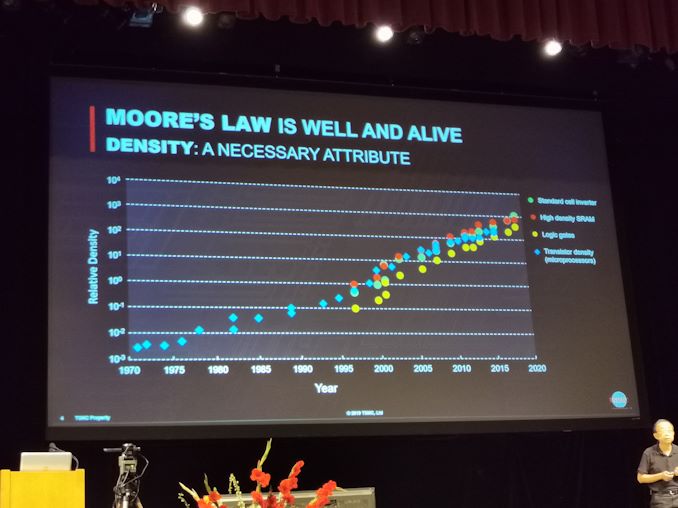

16:50 EDT – Kepadatan penting karena merupakan kekuatan pendorong utama untuk logika kinerja tinggi

16:50 EDT – Kepadatan masih pada lintasan log yang sama pada plot log linear

16:50 EDT – Bahkan hingga tahun 2020

04.54 EDT – Hukum Moore adalah hidup dan sehat. Siapa bilang itu mati? Kepadatan meningkat, dan akan meningkat

04.54 EDT – Atribut baru sedang diminta, seperti kecepatan atau efisiensi jam, yang Hukum Moore tidak pedulikan

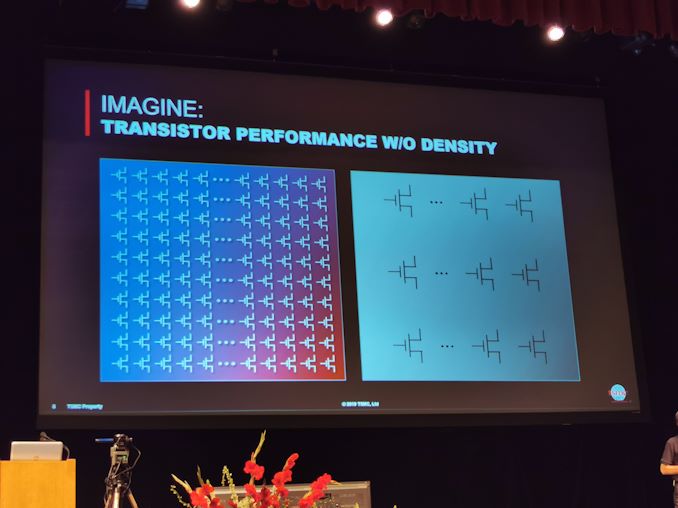

04:52 EDT – Kepadatan masih raja – memori, inti, akselerator

04:52 EDT – Penundaan kawat dengan transistor terbaik tidak ada artinya tanpa kepadatan

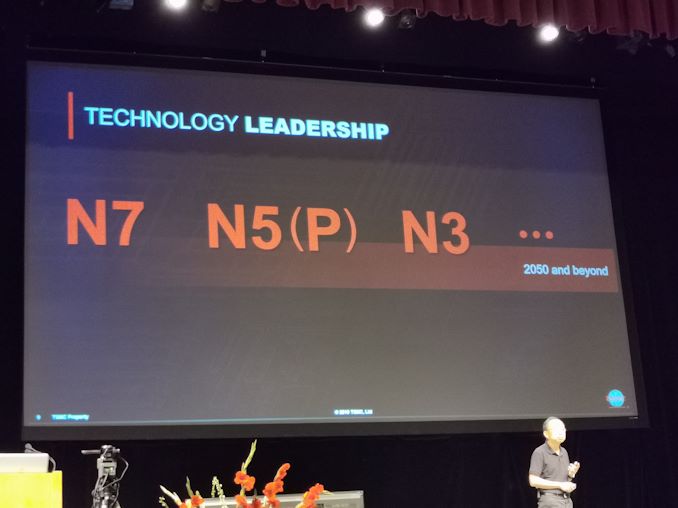

04:52 EDT – N7

04:53 EDT – Dunia Pertama 7nm

04:53 EDT – N5 (P) berikutnya, menggunakan EUV secara ekstensif, sudah dalam produksi risiko

04:53 EDT – Lalu N3

04.54 EDT – Nomor yang digunakan berarti sesuatu tentang fitur. Sekarang mereka hanya angka, seperti nomor model mobil

04.54 EDT – Jangan bingung nama node dengan teknologi yang sebenarnya ditawarkan

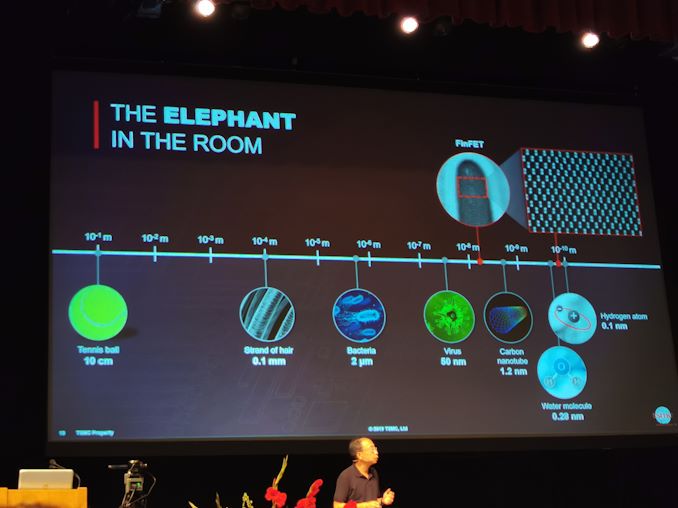

04.55 EDT – Sirip FinFET, atom mudah dihitung sekarang

04.55 EDT – Penskalaan dimensi 2D perlahan-lahan menjadi terbatas karena jumlah atom

16:56 EDT – Tetapi ukuran finfet bukan satu-satunya tombol yang dapat disetel untuk mengonfirmasi Hukum Moore

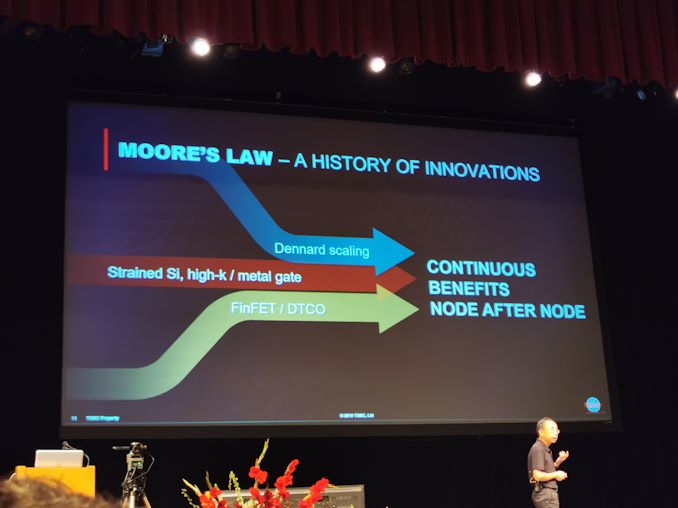

16:56 EDT – Strain Si, High-K, 2D ke 3D FinFET dll

16:56 EDT – Desain optimasi bersama

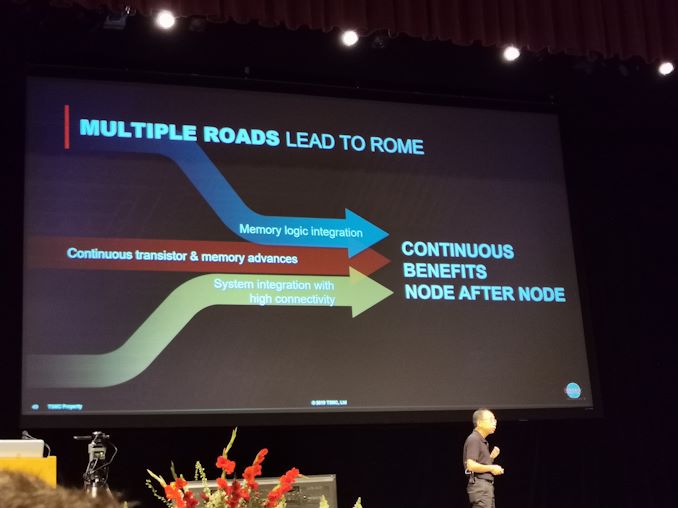

04:57 EDT – Manfaat berkelanjutan simpul demi simpul

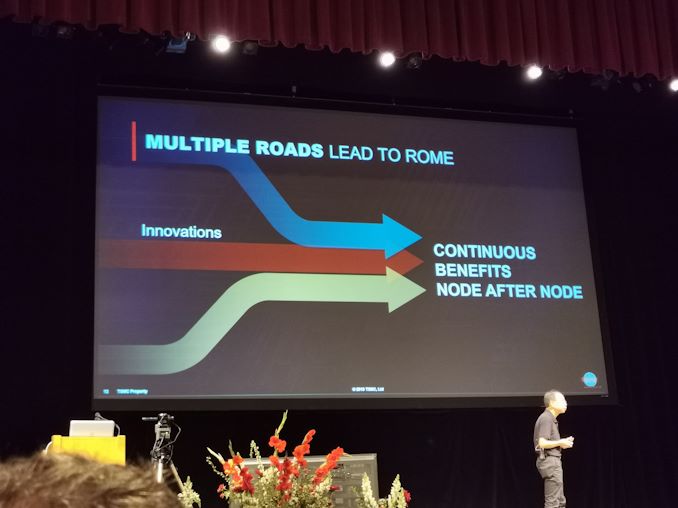

04:57 EDT – 'Banyak jalan menuju Roma'

04:57 EDT – Apakah itu referensi AMD?

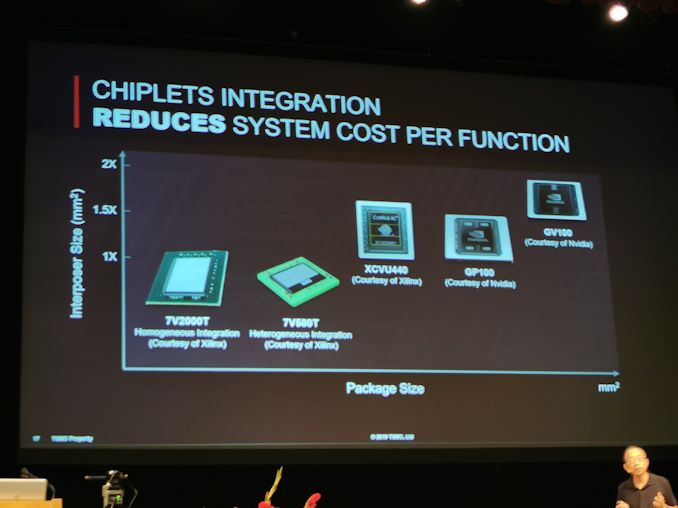

04:57 EDT – Di Moore's Paper, diprediksi chiplet

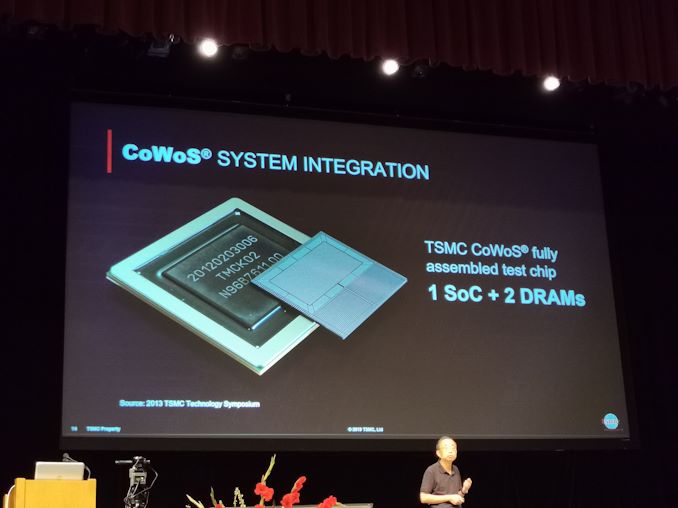

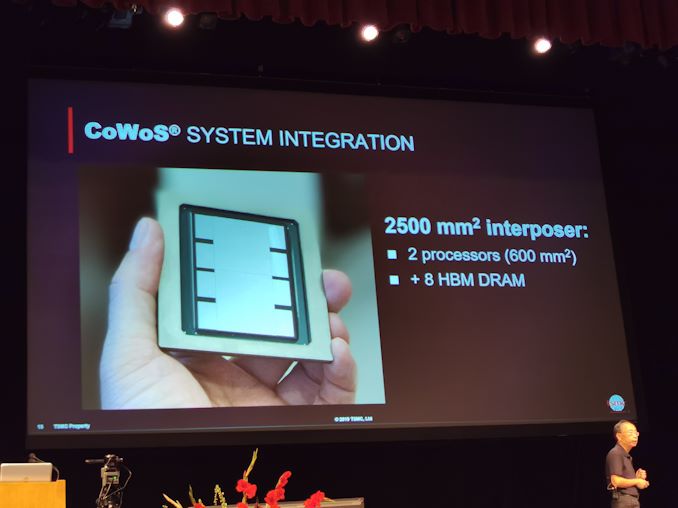

16:58 EDT – Di TSMC, Kontrak Kerja

16:58 EDT – Chip pada Wafer dari Substrat

04:59 EDT – Sebagian besar teknologi didorong inovasi sistem top-down saya, bukan dari bawah ke atas

05:00 PM EDT – Pindah ke era AI / 5G

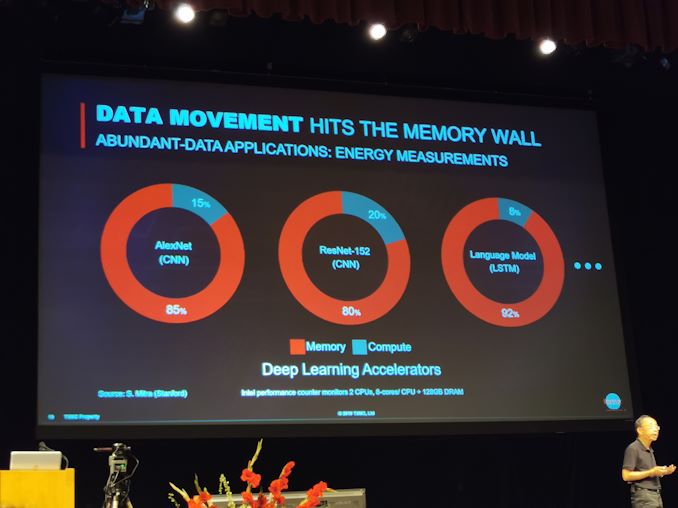

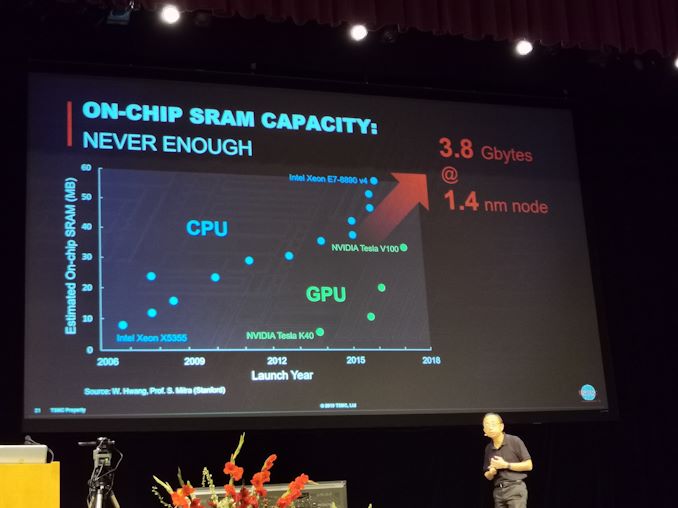

05:01 EDT – Pergerakan data berarti kita telah menabrak dinding memori

05:01 EDT – Hari ini, akses memori mengontrol efisiensi energi

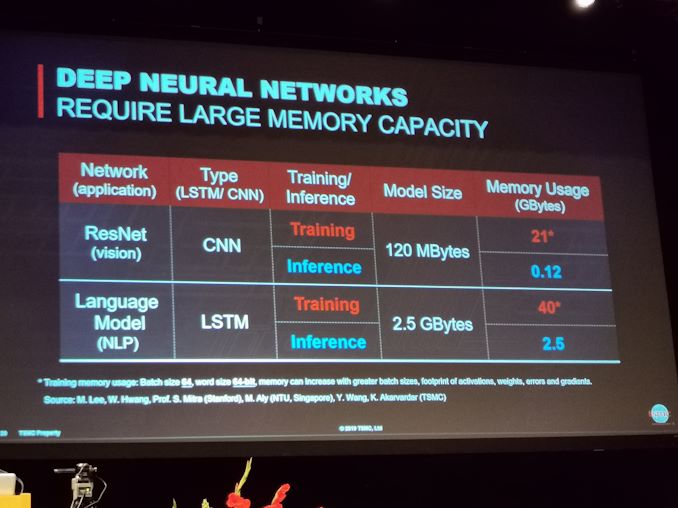

05:02 EDT – Deep Neural Networks membutuhkan kapasitas memori yang besar

05:02 EDT – Ini masalah hari ini. Masalah hari esok akan lebih menuntut memori

05:03 EDT – Perlu lebih banyak SRAM pada chip

05:03 EDT – Tidak akan pernah ada cukup SRAM pada chip, itu jelas

05:03 EDT – Bagaimana kita bisa menaruh banyak memori pada chip

05:04 EDT – Memori seperti apa yang penting

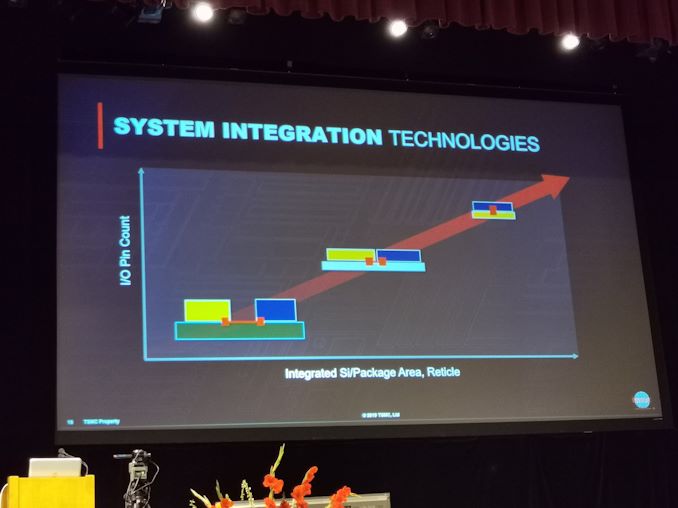

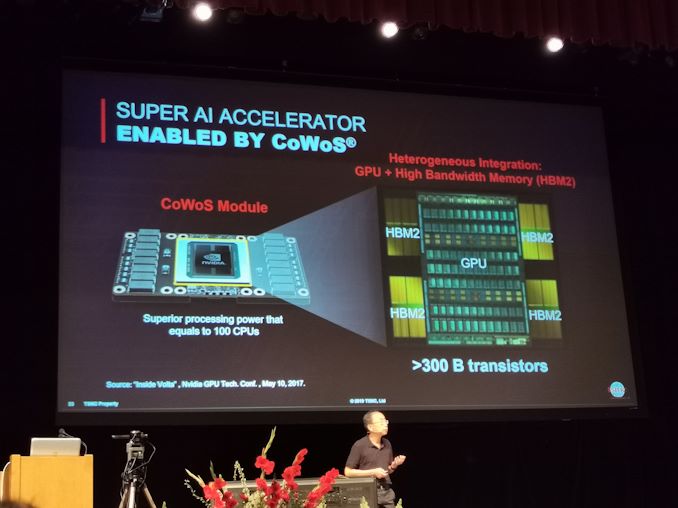

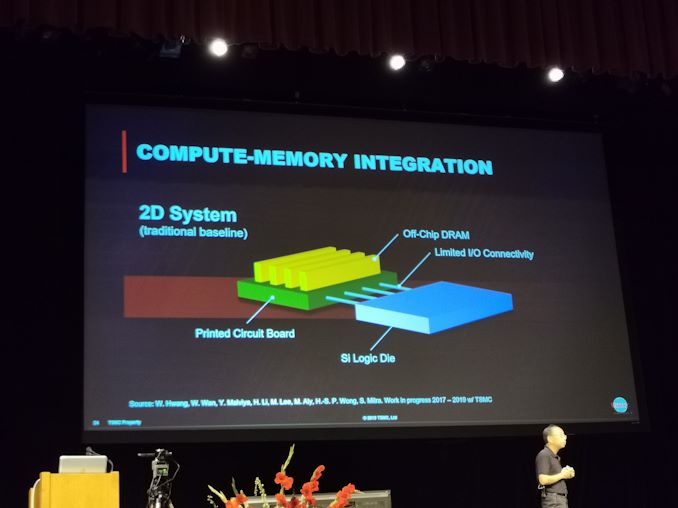

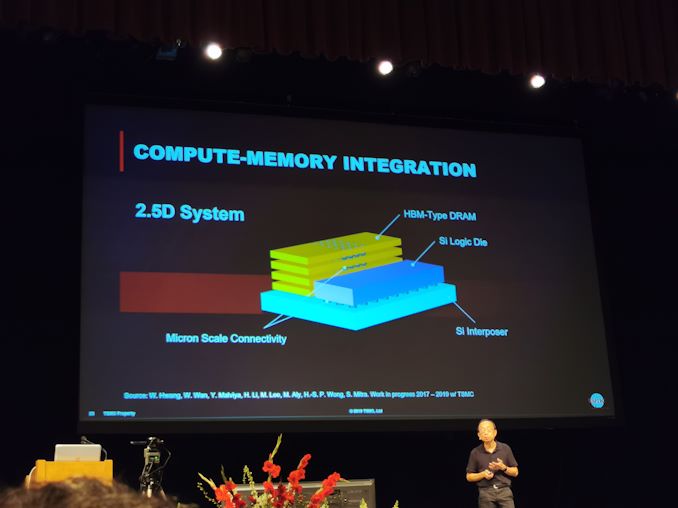

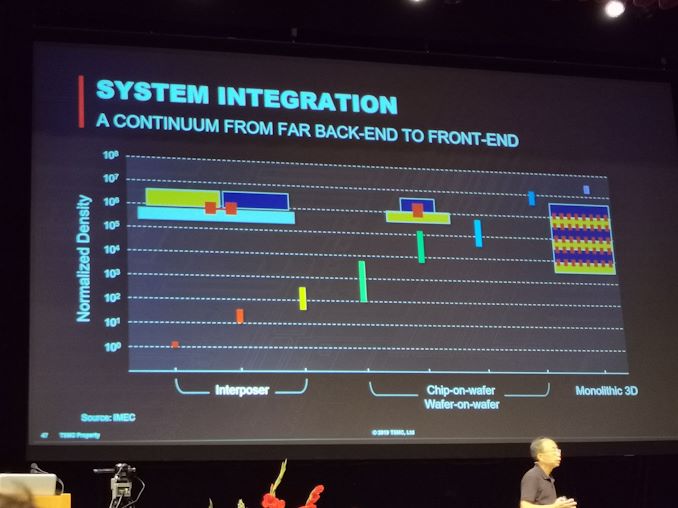

05:04 EDT – Berbagai sistem saat ini – 2D dan 2.5D

05:05 EDT – 2.5D menggunakan TSV

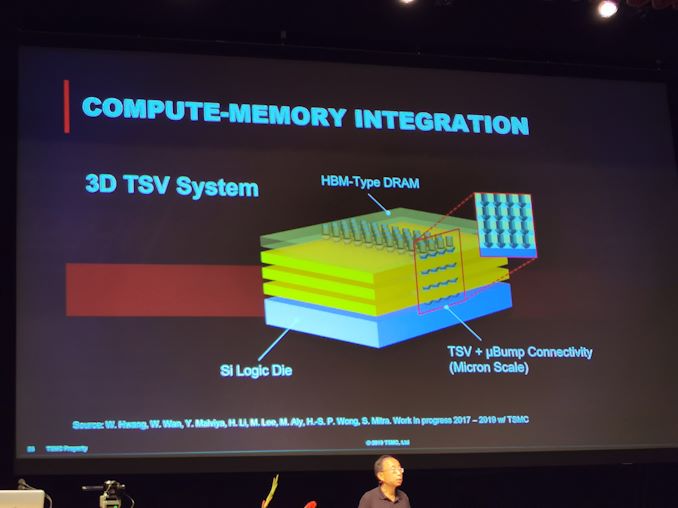

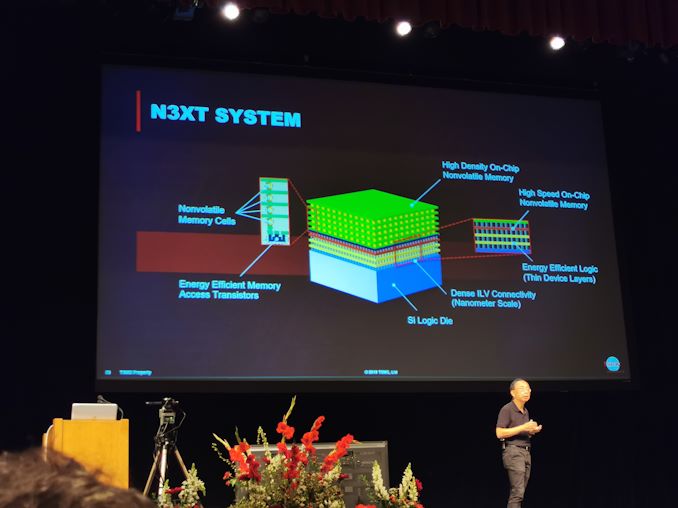

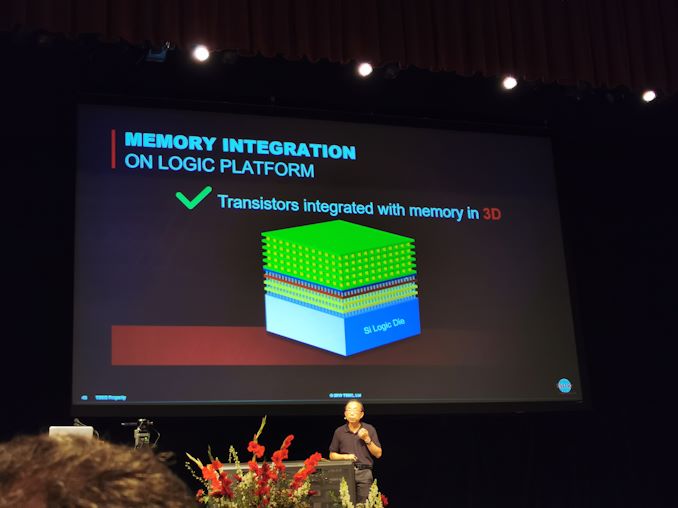

05:05 EDT – Satu langkah lebih jauh adalah 3D

05:06 EDT – Konektivitas meningkat lebih dari 2.5D dan 2D

05:06 EDT – Konektivitas pada urutan mikron bahkan tidak cukup

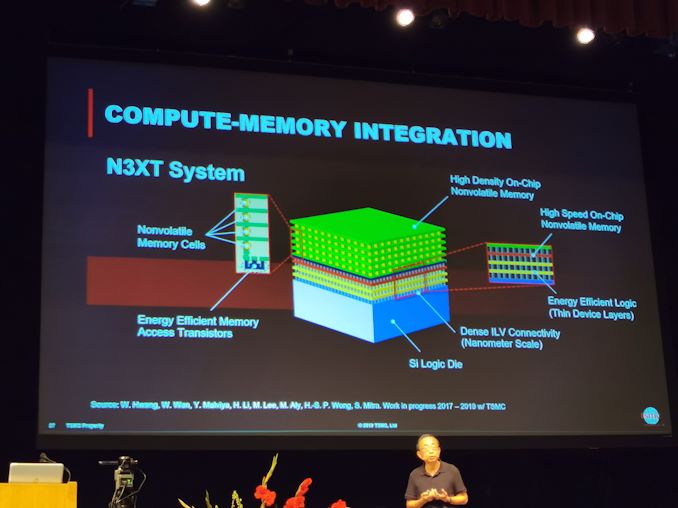

05:07 EDT – Beyond 3D menggabungkan logika dan memori dan mengintegrasikannya

05:07 EDT – Beberapa lapisan memori dan logika

05:07 EDT – TSV padat, atas perintah nm

05:07 EDT – Ini adalah sistem level 'N3XT'

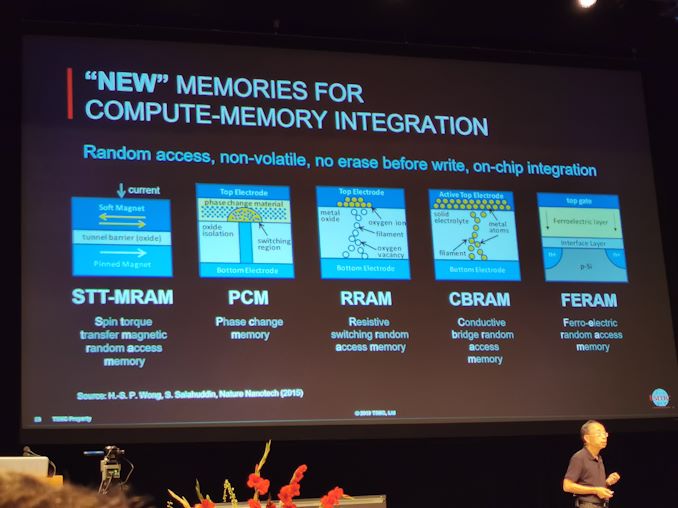

05:08 EDT – Banyak kenangan baru untuk menyelesaikan masalah ini

05:08 EDT – STT-MRAM, PCM, RRAM, CBRAM, FERAM

05:09 EDT – Banyak dari mereka sudah dalam produk

05:09 EDT – MRAM 22nm misalnya

05:09 EDT – Integrasi on-chip penting

19.11 EDT – harus dilakukan pada suhu rendah

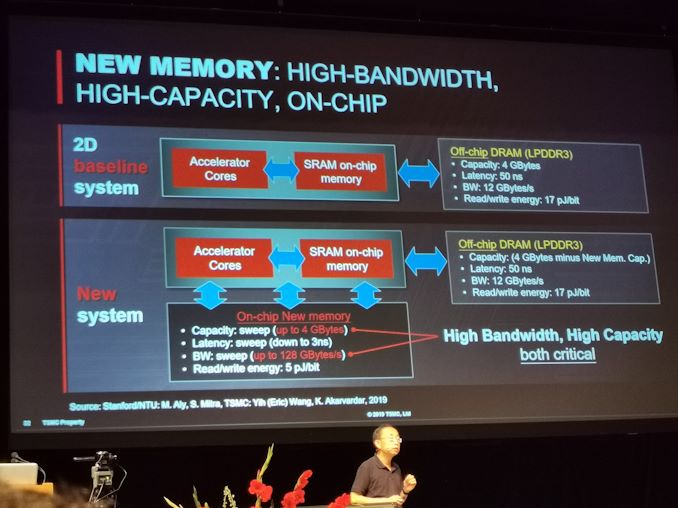

19.11 EDT – Memori baru harus bandwidth tinggi, kapasitas tinggi, dan pada chip

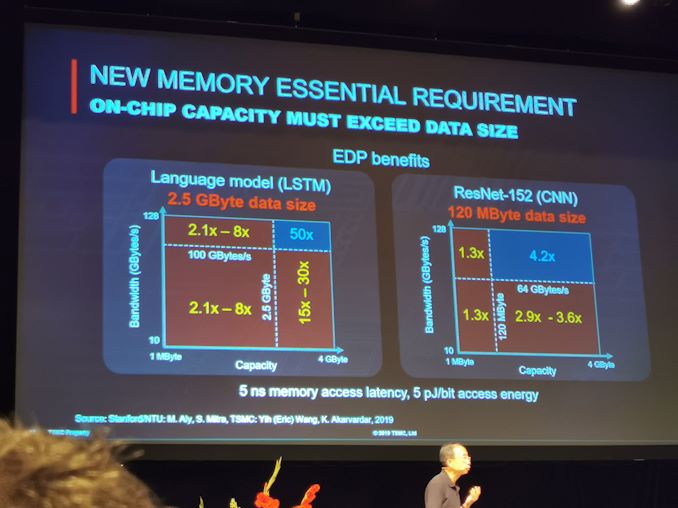

05:13 PM EDT – Kapasitas chip harus melebihi ukuran data

05:13 PM EDT – Grafik ini menunjukkan speedup potensial

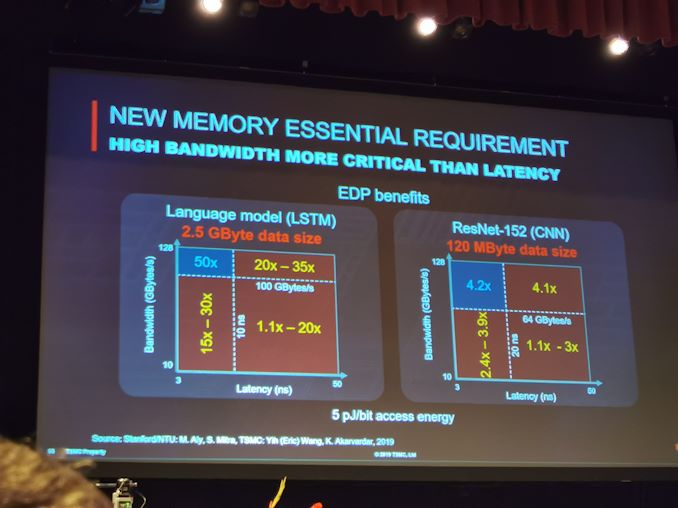

05:14 PM EDT – Lebih banyak bandwidth seringkali lebih penting daripada latensi

19:15 EDT – Jadi memori baru harus memiliki bandwidth tinggi dan kapasitas tinggi untuk pelatihan model

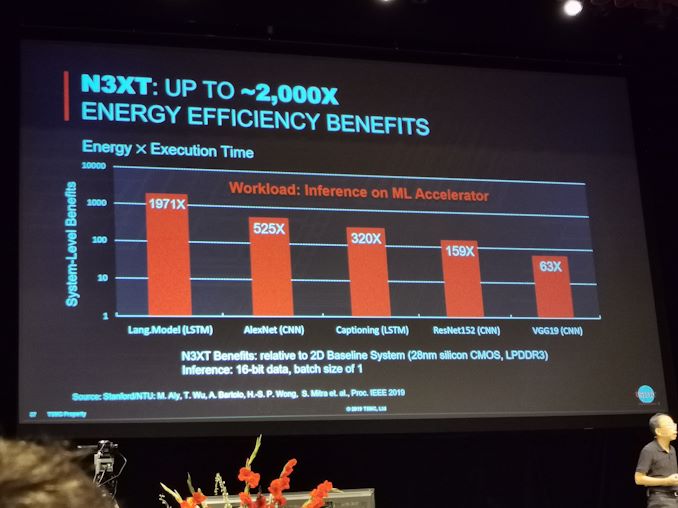

05:16 PM EDT – Dapat melakukan riset untuk melihat manfaat hingga 2000x dengan memori yang cukup pada chip dengan bandwidth yang cukup tinggi dengan integrasi logika-memori yang ketat

05:17 EDT – Banyak memori membutuhkan banyak logika yang harus disatukan satu sama lain

05:17 EDT – Tidak mungkin dengan teknologi saat ini

05:17 EDT – Sulit untuk membangun transistor perf tinggi pada lapisan atas karena memerlukan> 1000C pada manufaktur, yang menurunkan lapisan memori

05:18 PM EDT – Perlu lapisan perangkat tipis dan suhu fabrikasi rendah untuk membangun sistem yang ideal ini

05:19 PM EDT – Teknologi Transistor telah mengalami banyak kemajuan baru-baru ini

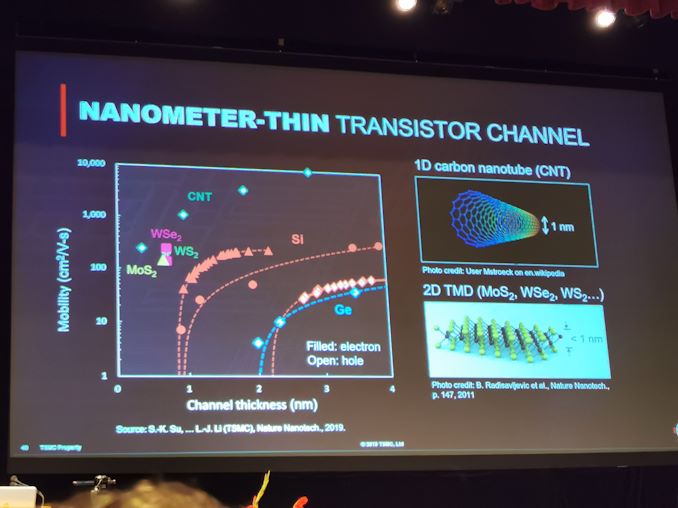

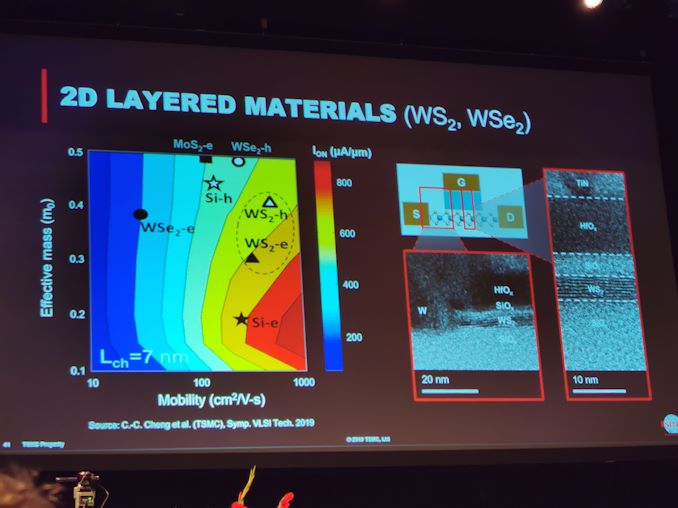

19.20 EDT – Bahan berlapis 2D, seperti Desain Logam Transisi 2D TMD (MoS2, WSe2, WS2)

19.20 EDT – atau bahan 1D, seperti Carbon Nanotube

19.20 EDT – Bahan-bahan ini memiliki mobilitas pembawa yang tinggi, dan sangat tipis

17:21 EDT – Membuat ketebalan saluran lebih kecil, tetapi menjaga mobilitas tinggi

17:21 EDT – Ini adalah slide yang penting

17:22 EDT – Ada hampir 2000 opsi TMD, perlu memilih yang terbaik

17:22 EDT – Juga perlu memiliki massa efektif yang masuk akal

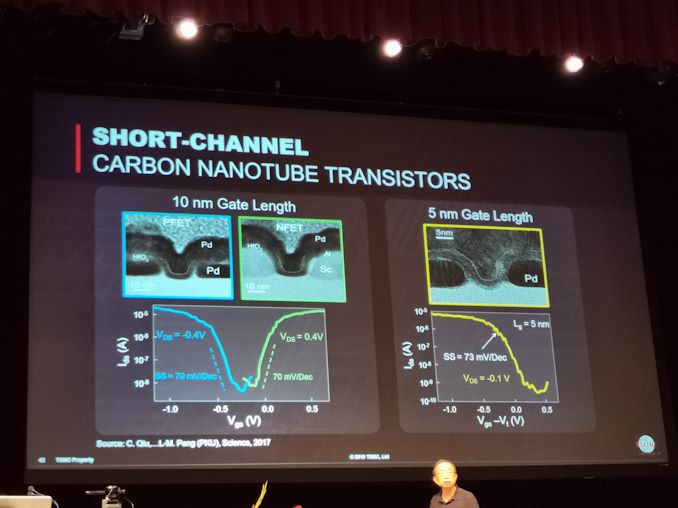

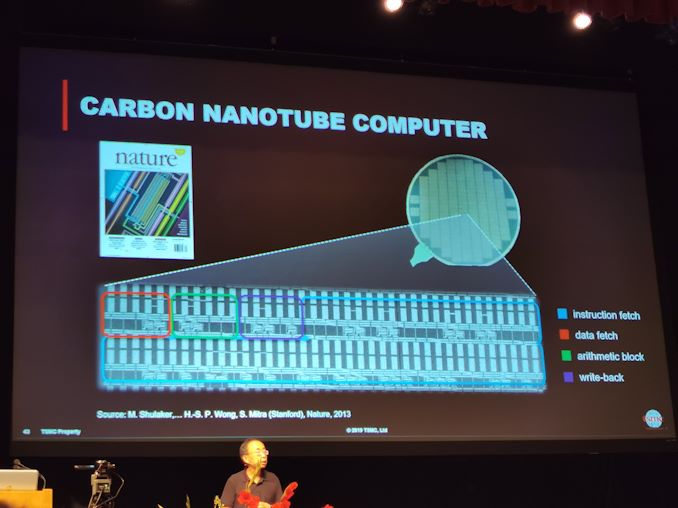

17:23 EDT – Sekarang 1D

17:23 EDT – CNT sudah sekitar 20 tahun

17:24 EDT – 20+

17:24 EDT – CNT memiliki karakteristik yang sangat baik untuk transistor

17:24 EDT – Telah menunjukkan komputer lengkap berjalan di CNT tanpa silikon

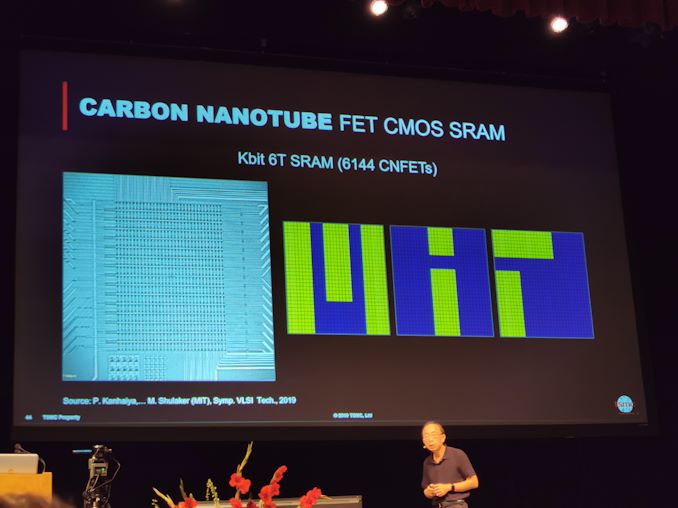

19.25 EDT – Juga ditunjukkan SRAM 6T yang dibangun dari CNT

19.25 EDT – 6144 CNFET

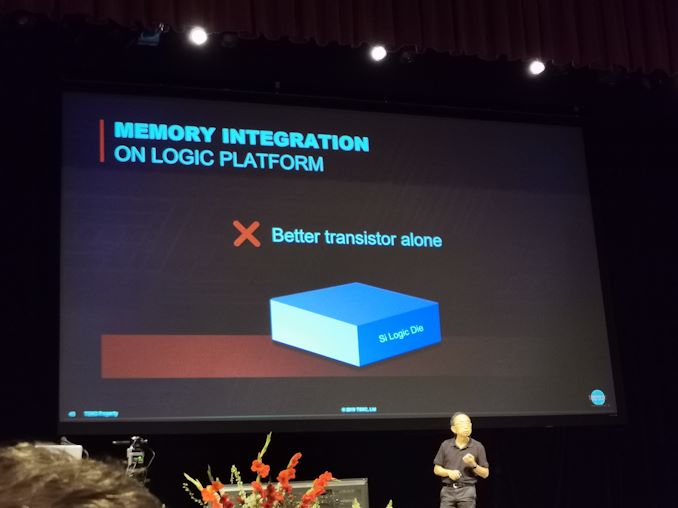

17:26 EDT – Secara keseluruhan, Anda tidak hanya membutuhkan transistor yang lebih baik, Anda membutuhkan integrasi yang lebih baik dengan memori

17:27 EDT – Gunakan berbagai teknik integrasi sistem. Itu sebuah kontinum

17:28 EDT – Teknologi canggih adalah pembeda utama

17:30 EDT – Panggilan untuk bertindak: keterlibatan awal antara insinyur sistem dan pengembangan teknologi

17:30 EDT – Perlu interaksi yang lebih dekat antara teknologi perangkat dan persyaratan

1931 EDT – Academia perlu bekerja sama dengan riset industri, lebih banyak hari ini daripada sebelumnya

1931 EDT – Waktu tanya jawab

05:32 PM EDT – T: Variabilitas dalam SRAM CNT? A: Ya di koran. Hari ini kami dibatasi oleh kemampuan hebat universitas. Variabilitas disebabkan oleh ketidakmampuan mengendalikan di universitas. Variabilitas tidak akan jauh berbeda dari silikon komersial tetapi lebih halus

05:36 PM EDT – T: Komputasi memori analog mungkin tidak memiliki masa depan? A: Saya tidak punya informasi khusus tentang komputasi analog, tetapi kepadatan perangkat penting. Salah satu caranya adalah integrasi 3D dari logika dan memori. Kepadatan itulah yang mendorong Hukum Moore. Kita perlu memberikan kepadatan perangkat dan kepadatan konektivitas dan itu akan tetap penting.

05:39 PM EDT – T: Bagaimana cara perusahaan perangkat lunak bekerja dengan TSMC di masa depan? A: Pengembangan logika dan memroy agak terpisah di masa lalu, sehingga teknologi memori dan memori yang hebat perlu digabungkan kembali. Ini akan menjadi masalah komputasi yang harus dapat digunakan oleh perangkat lunak. Buat itu layak sementara, seperti MRAM 22nm, atau 22 RRAM. Dibutuhkan keterlibatan awal antara penelitian dengan tampilan sistem dan terlibat dengan sisi teknologi, bersama-sama kita bisa mencari tahu apa campuran teknologi yang tepat

05:39 PM EDT – Itu bungkus. Pembicaraan berikutnya adalah Gen-Z