Trang web này có thể có được hoa hồng liên kết từ các liên kết trên trang này. Điều khoản sử dụng.

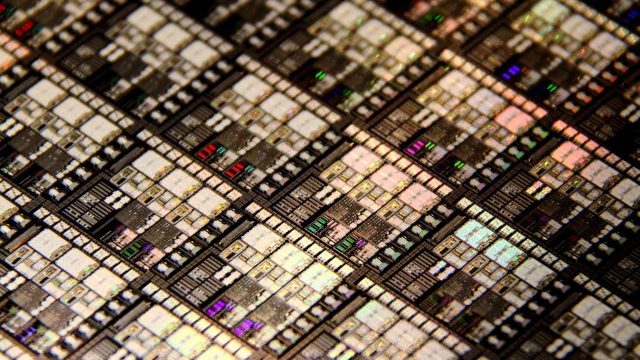

Ảnh: Getty Images

Số lượng bóng bán dẫn CPU hiện đại là rất lớn: AMD đã công bố đầu tháng này rằng việc triển khai đầy đủ CPU Epyc "Rome" từ 7 nm nặng 32 tỷ bóng bán dẫn. Đối với điều này, Cerebras Technology nói: "Giữ bia của tôi." Công ty tập trung vào AI đã thiết kế cái mà họ gọi là Máy đo tỷ lệ wafer. WSE là một hộp, khoảng tám inch x 9 inch, và chứa khoảng 1,2 bóng bán dẫn nghìn tỷ.

Tôi đã rất ngạc nhiên khi thấy một công ty đưa sản phẩm quy mô wafer vào thị trường này một cách nhanh chóng. Ý tưởng xử lý quy mô wafer gần đây đã được chú ý như là một giải pháp khả thi cho những khó khăn của hiệu suất mở rộng. Trong nghiên cứu mà chúng tôi đã thảo luận vào đầu năm nay, các nhà nghiên cứu đã đánh giá ý tưởng xây dựng GPU lớn trên hầu hết các tấm wafer 100mm. Họ phát hiện ra rằng kỹ thuật này có thể tạo ra một bộ xử lý hiệu năng cao khá tốt và cũng có thể mở rộng hiệu quả đến kích thước nút lớn hơn. WSE của Cerebra chắc chắn đủ điều kiện là lớn: tổng diện tích lớn hơn nhiều so với thiết kế giả thuyết mà chúng tôi đã xem xét vào đầu năm nay. Đây không phải là một wafer 300mm kích thước đầy đủ, nhưng nó có diện tích bề mặt lớn hơn 200mm.

GPU lớn nhất, Chỉ để so sánh, đo 815 milimet vuông và đóng gói bóng bán dẫn 21.1B. Vì vậy, Cerebras WSE chỉ là một một chút lớn hơn, khi những điều này tiến triển. Một số công ty gửi ảnh chip của họ cùng với một đối tượng chung nhỏ, chẳng hạn như đồng xu. Cerebras gửi hình ảnh súc sắc của mình đến bàn phím.

Chỉ để so sánh, đo 815 milimet vuông và đóng gói bóng bán dẫn 21.1B. Vì vậy, Cerebras WSE chỉ là một một chút lớn hơn, khi những điều này tiến triển. Một số công ty gửi ảnh chip của họ cùng với một đối tượng chung nhỏ, chẳng hạn như đồng xu. Cerebras gửi hình ảnh súc sắc của mình đến bàn phím.

Không có ảnh: khe cắm PCIe x1600.

Như bạn có thể thấy điều này so sánh khá tốt.

Cerebras WSE chứa 400.000 hạt nhân đại số tuyến tính hiếm, 18GB tổng bộ nhớ mảng, 9PB / giây băng thông bộ nhớ giữa các chip và băng thông mô riêng biệt lên tới 100Pbit / giây. Tất cả các chip được xây dựng trong quy trình 16nm FinFET TSMC. Do các chip này được xây dựng từ (hầu hết) các tấm riêng lẻ, công ty đã thực hiện một phương pháp định tuyến xung quanh các lõi bị lỗi trong mảng và có thể giữ các mảng được kết nối ngay cả khi chúng có các lõi bị lỗi trong phần wafer. Công ty cho biết họ đã thực hiện một mảng ma trận dự phòng, mặc dù nó chưa được thảo luận cụ thể. Chi tiết về thiết kế được giới thiệu trong Hot Chips tuần này.

WSE: "CPU" dường như không đủ – nó làm mát bằng cách sử dụng các tấm lạnh lớn ở trên silicon, với các ống nước được gắn theo chiều dọc được sử dụng để làm mát trực tiếp. Do không có gói truyền thống đủ lớn để lắp chip, Cerebras đã tự thiết kế nó. PCWorld mô tả nó là "sự kết hợp của PCB, tấm wafer, đầu nối đặc biệt kết nối cả hai và tấm lạnh". Thông tin chi tiết về chip, chẳng hạn như hiệu suất gộp và mức tiêu thụ năng lượng, vẫn chưa có sẵn.

Một bộ xử lý quy mô wafer đầy đủ chức năng, được bán trên thị trường ở quy mô, sẽ là một minh chứng thú vị về việc phương pháp công nghệ này có phù hợp với thị trường rộng lớn hơn hay không. Mặc dù chúng ta sẽ không bao giờ thấy các thành phần tiêu dùng được bán theo cách này, nhưng có mối quan tâm trong việc sử dụng quy trình xử lý wafer để cải thiện hiệu suất và tiêu thụ điện năng ở các thị trường khác nhau. Nếu người tiêu dùng tiếp tục chuyển khối lượng công việc lên đám mây, đặc biệt là khối lượng công việc hiệu suất cao như chơi game, sẽ không điên rồ khi nghĩ rằng một ngày nào đó chúng ta có thể thấy các nhà sản xuất GPU tận dụng ý tưởng này và xây dựng một số thành phần không phải là tất cả có thể làm để hỗ trợ sistema của trò chơi đám mây trong tương lai.

Bây giờ đọc: