03,39 EDT -.

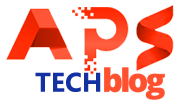

03:05 EDT: Một trong những sản phẩm 10nm trong tương lai của Intel là công cụ suy luận Spring Hill NNP-I 1000. Hôm nay, công ty nâng nắp trên một phần của kiến trúc đằng sau con chip.

03:05 EDT – Đây là chip 10nm!

03:05 EDT – Sắp có thêm thông tin. Họ nói với tôi về điều này

03:06 EDT – Tôi vẫn không có thời gian để viết nó. Nhưng đây là blog trực tiếp.

03:07 PM EDT – Tầm quan trọng của học máy và kết luận

03:07 PM EDT – Kiến trúc chip rất quan trọng

03:09 PM EDT – Một chip Intel nội bộ thuần túy

03:09 PM EDT – Có mặt ở yếu tố hình thức M2 và các yếu tố hình thức đặc biệt

03:10 PM EDT – Mô-đun M.2 hiển thị trang bị DRAM 16 GB trên tàu

03:10 chiều EDT – 5 vài phút và vẫn trên slide giới thiệu

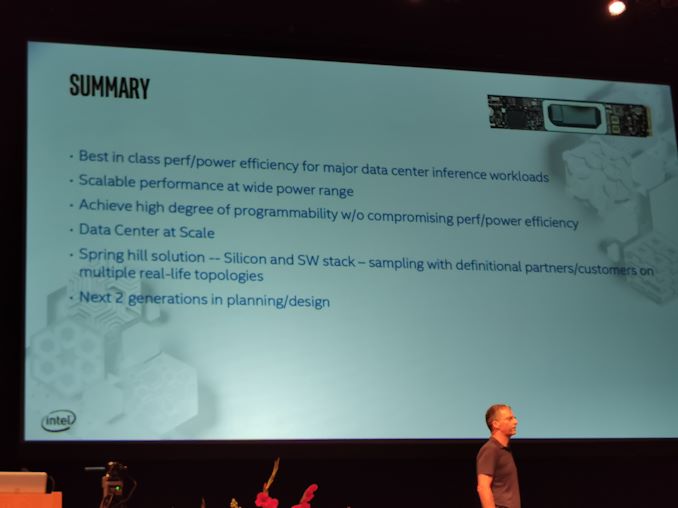

03:11 PM EDT – Cho đến khi 4,8 ĐẦU / W

03:11 PM EDT: cùng một silicon có thể đạt 10W đến 50W

03:11 PM EDT – Đây là chip DC

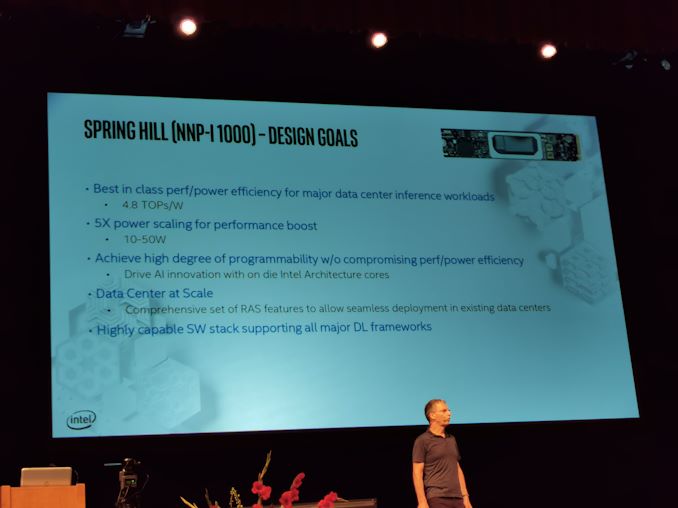

03:11 PM EDT – Chứa lõi Intel Sunny Cove

03:11 PM EDT: Stack SW hỗ trợ tất cả các khung DL chính

03:11 PM EDT: Có Sunny Cove có nghĩa là AVX-512 trên tàu

03:14 EDT – Tính năng RAS cho DC

15:15 EDT – Vẫn trên slide này

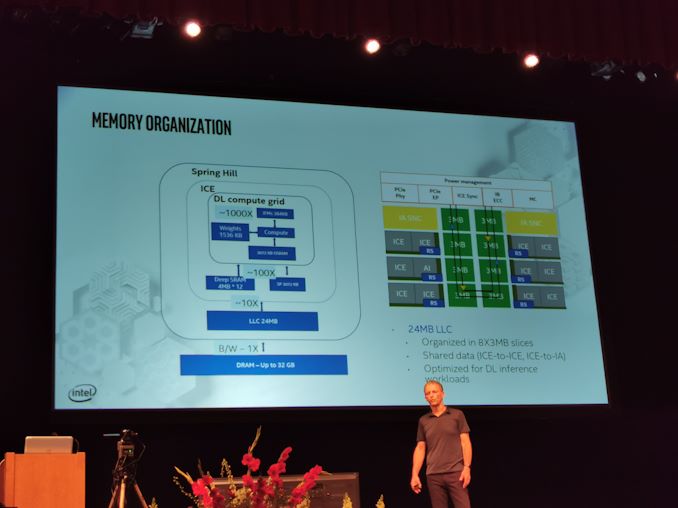

03:16 chiều EDT – 2 Sunny Cove Cores, 12 Trung tâm suy luận, 24 MB chia sẻ bộ nhớ cache

03:16 PM EDT – ’ES. Nhưng không phải hồ ICE

03:16 PM EDT – Về cơ bản, đây là con chip 8 nhân Ice Lake có đồ họa và 6 loại bỏ lõi và ICE di chuyển

03:17 PM EDT: hỗ trợ DRAM tương tự như Ice Lake

15:18 EDT: Mỗi lõi của Sunny Cove có thể điều khiển một trong 12 Lõi băng này

15:18 EDT: Kết nối PCIe 3.0 x4 / x8 để lưu trữ CPU

15:18 EDT – Tổng SRAM 75MB, BW DRAM 68 GB / s

15:19 EDT: hơn 10 đỉnh quá trình

15:19 EDT: được thiết kế cho các sự cố với nguồn điện hạn chế

15:19 EDT: Quản lý năng lượng giống như Ice Like

15:19 EDT – Hồ

03.20 EDT – Gán khối lượng công việc cho ngân sách năng lượng được giao

03.20 EDT – Thiết bị PCIe tiêu chuẩn

03:21 EDT: Ở chế độ 50W, nó chắc chắn không phải là ổ M.2

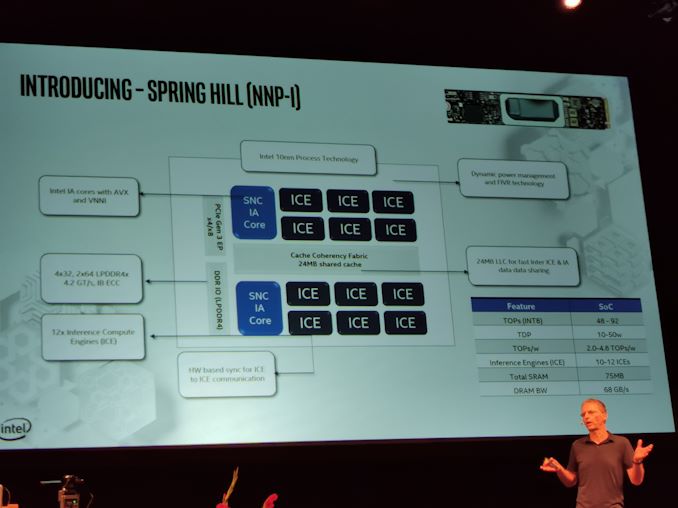

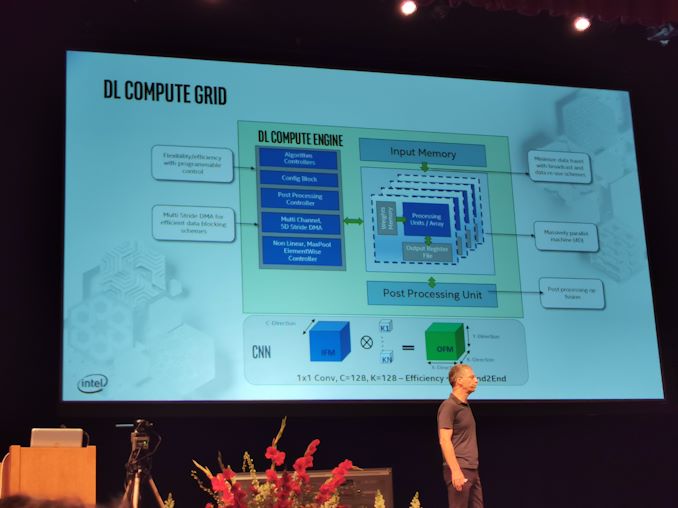

15:22 EDT – Mỗi ICE có thể thực hiện 4K MAC / chu kỳ

03:23 EDT – Hỗ trợ FP16 / INT8 / 4/ /2/ /1

03:23 EDT – DMA được tối ưu hóa đặc biệt cho DL

03:23 EDT – Đơn vị nén / giải nén cho độ hiếm

03:24 EDT – 4 MB SRAM qua ICE với 256KB TCM giữa Compute Grid / Vector DSP

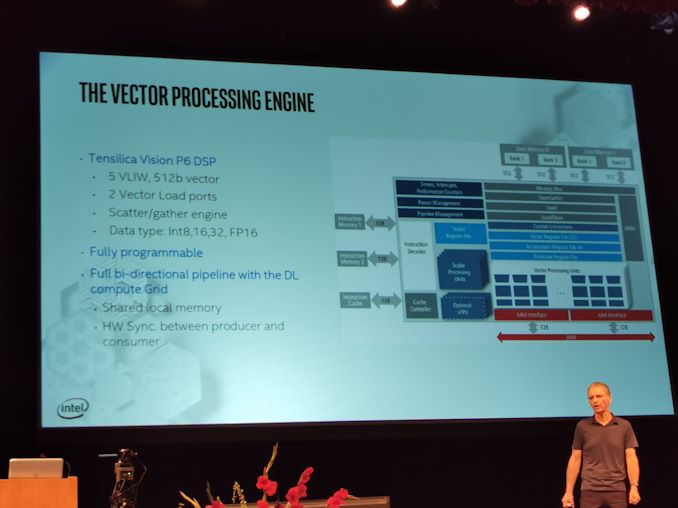

3: 24 EDT – Tensilica V6 DSP của ICE

15:25 EDT – Máy tính DL trông giống như một hộp 4D

15:25 EDT – Bước tiến DMA 5D

15:25 EDT – Xử lý hậu phẫu

03:26 EDT – Giảm thiểu truyền dữ liệu

03:26 EDT – Bộ điều khiển phi tuyến ElementWise Maxpool

03:28 PM EDT – DSP có 2 cổng sạc vector, hỗ trợ động cơ phân tán / thu gom gốc

03:28 PM EDT – Hoàn toàn có thể lập trình

03:28 PM EDT – đường ống hai chiều với điện toán lưới DL với bộ nhớ cục bộ và đồng bộ hóa phần cứng

03:28 chiều EDT – 4 mức bộ nhớ

03:29 EDT – Nó giống như lõi 8 băng với các hạt nhân bị xé toạc 2 Đã nhập ICE

3: 29 EDT – DRAM lên đến 32 GB

03:29 EDT – Không hỗ trợ BF16

03:30 EDT – ResNet-50, 3.600 suy luận mỗi giây ở mức 10W

03:31 PM EDT – Mẫu trung tâm 2 lên đến 12 cung cấp tốc độ 585x

03,39 EDT – Đó là một bọc. Giờ ăn trưa Tiếp theo là TSMC Keynote lúc 1:45 chiều PT.